|

|

发表于 2020-6-25 20:58:47

|

显示全部楼层

发表于 2020-6-25 20:58:47

|

显示全部楼层

本帖最后由 bg1trk 于 2020-6-25 21:03 编辑

我知道降低输出阻抗可以减少干扰,请教一下降低输出阻抗起什么作用(什么原因)。

试着解释,您把传输线理解为天线,同样强度的空间杂散干扰,这段“天线”如果对地阻抗很高就会感应出较高的噪声,降低阻抗,感应噪声随之降低。极限情况是接地,噪声为零。

信号入口就近对地接电阻,是为了降低输入阻抗吧,信号出口对地接电阻起什么作用?

高频信号在阻抗不匹配的节点会形成反射,两个运放“接力”,严格的说应该在后面运放的入口加电阻。我习惯在出入口都留焊盘,有时候在出口处加个电阻也有效果,有点玄学。

上个回帖说的有点乱,前面说的是您用PWM做DA转换,没加跟随输出阻抗较高比较容易引入干扰,板子布线要注意。从回帖了解到这方面您考虑到了。

后面是针对您临时改用DAC芯片来调试说的,猜测临时调试时飞了线,主要是想表达对较长飞线的处理。

电感这事还在犯难,举棋不定。想最大电流不容易,有点想放弃。

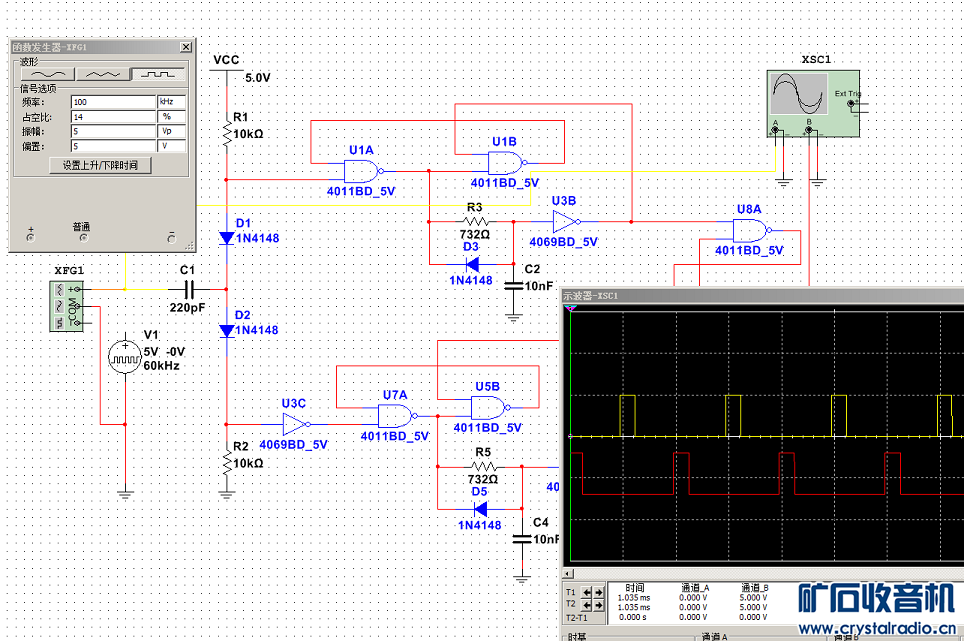

仅有的进度是参考别人的电路用门电路搭了个180度移相器,仿真通过了,表现良好。494之类的芯片加两片CD4011做交错并联,有点实现的可能了。

|

评分

-

1

查看全部评分

-

|