|

|

发表于 2023-4-17 10:04:49

|

显示全部楼层

发表于 2023-4-17 10:04:49

|

显示全部楼层

本帖最后由 天天爱玛丽 于 2023-4-17 10:36 编辑

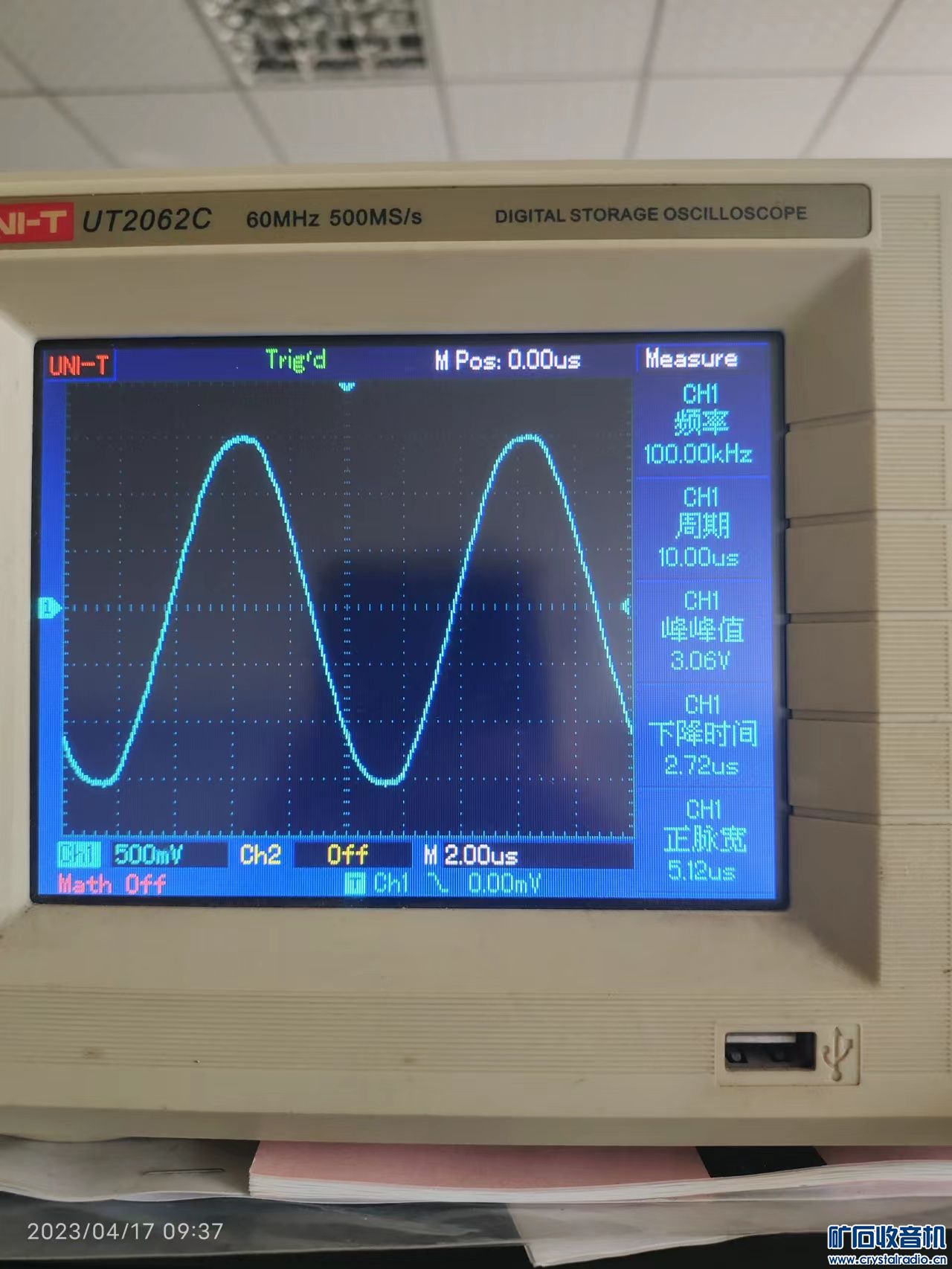

测试了一下开启和关闭DAC缓冲器的波形,

用的定时器触发DMA方式,定时器自动重载值8,VDDA=3.3V,12bit,采样点40,对应100KHz,

从手册中查到DAC的C_out_load = 50pf,这个电容和负载阻抗的时间常数t,会影响到DAC输出电压,

在开启DAC缓冲器时,由于每一个采样周期DAC的输出电压保持不变,t的影响较小,输出电压峰峰值比较高,

手册只给出了基本参数,开启缓冲器时DAC_OUT高端值会小于3.3V-0.2,DAC_OUT低端会大于50mV

也就是小于3.3v-0.2v-0.05v=3.23v,实际测量DAC_OUT峰峰值3.06V,

上图的波形峰峰值比较高,但是由于缓冲的存在,会产生失真,例如峰值两侧,可以明显观察到,

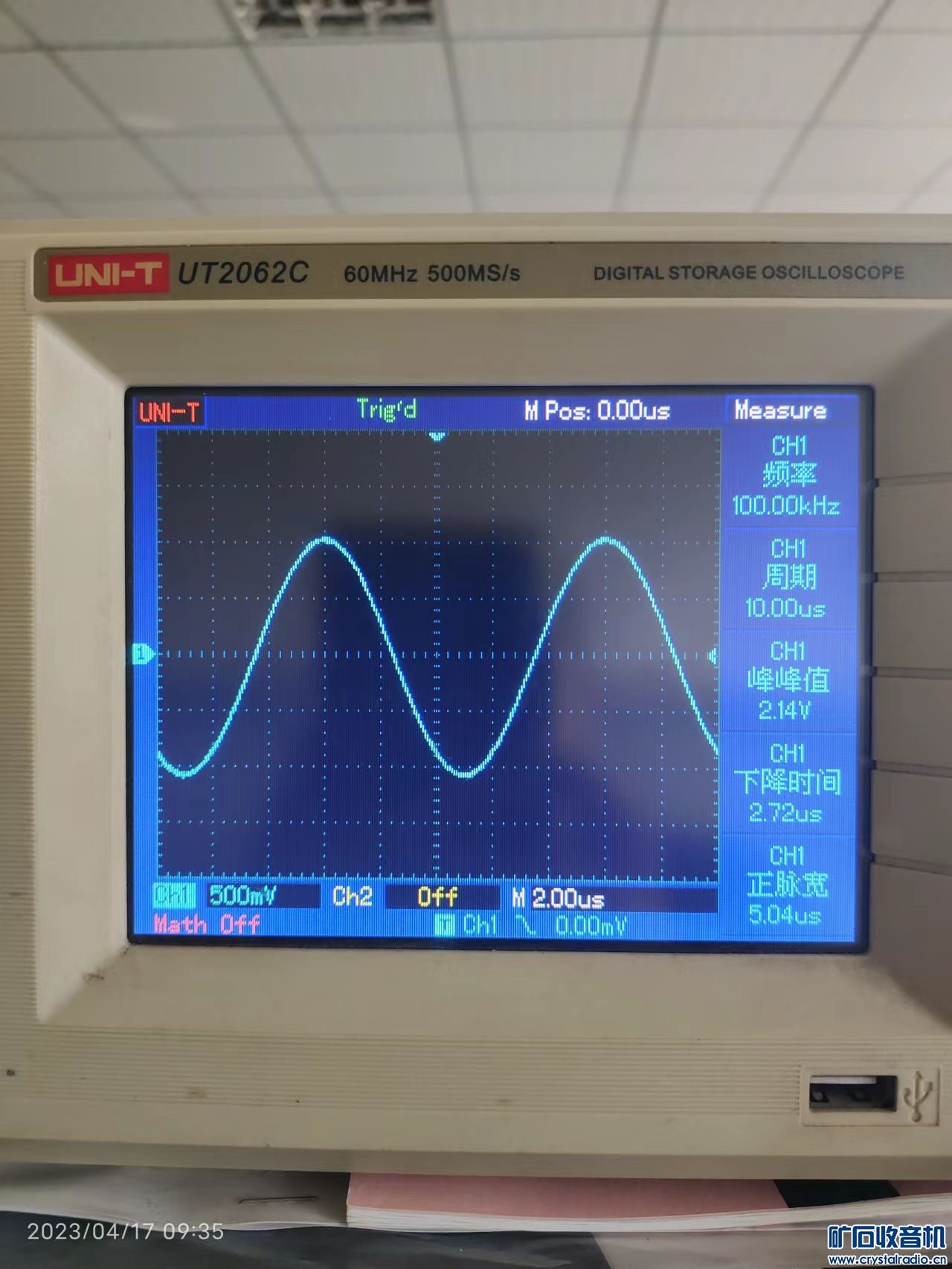

关闭DAC缓冲器时,C_out_load对输出幅度的影响就很明显了,

上图DAC峰峰值只有2.14V,离Vref的范围相差甚远.但是波形失真较小.

所以用于输出可调直流时建议开启缓冲器,用于输出音频时建议关闭缓冲器,

由此推断,每片芯片的DAC输出值都可能不同,

用于测量时可以用ad脚检测DAC的输出值,计算出误差,然后计算时进行补偿.

手册里说明了VDDA为ADC、复位、RC振荡器和PLL模拟部分供电,所以为了保持VDDA的纯净,要使用外部晶振,不要用内部RC时钟。

内部参照电压可以计算Vref,无法计算DAC的误差吧,DAC输出误差似乎是硬件差异造成的.

------------

air32f10x的DAC连续输出时存在一个+-10mV的波动,频率大概在7.94Hz,这是什么鬼? |

|