|

|

发表于 2024-8-20 15:39:47

|

显示全部楼层

发表于 2024-8-20 15:39:47

|

显示全部楼层

本帖最后由 MF35_ 于 2024-8-20 16:57 编辑

我之前看过一个国外大牛的高速PCB设计讲座,其中谈到过这个问题,他的原意是:

电源退耦的同一个点上,切忌使用大小电容并联,如果同一个电源线上存在不同大小甚至不同种类的电容时,它们要相距一定的距离,比如一块PCB的电源入口和芯片的供电引脚,它们的退耦电容可以不同。但在同一点,如果一定要并联,比如需要降低ESR或者电容的容量受限(众所周知二类介质的MLCC有非常糟糕的压电效应,容量越大越明显,所以很多场合会用多个小容量的并联),必须并联相同的电容。

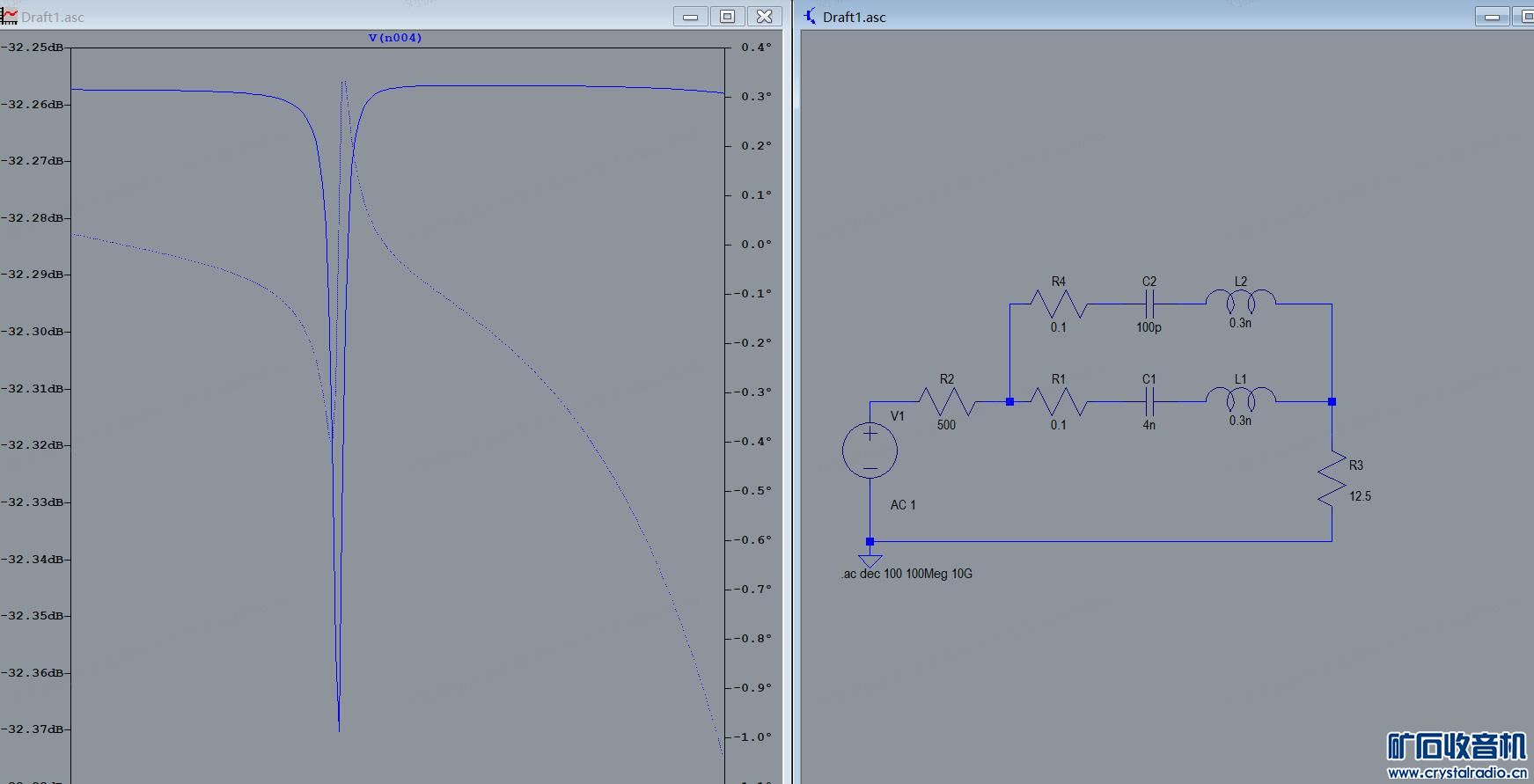

仿真可以看到相同电容并联是没有反谐振的

不过这个问题一般出现在GHz以上时比较明显,而且谐振峰很小(取决于ESR和ESL),并联小电容可以在百M到1G的范围提供更高一些的抑制,我之前做一个有源滤波器,截止频率10k以内,因为10uF这个级别的钽电容手头没有低ESR的,就并了47nF的NP0,从仿真和测试结果都发现从几十M开始到几百M(只能测到这么多)区间的带外抑制降低了几个dB

所以如果应用本身不关心GHz以上频率,也是可以并的,但原则是单个电容能够满足性能的前提下,尽量用单个电容 |

评分

-

5

查看全部评分

-

|